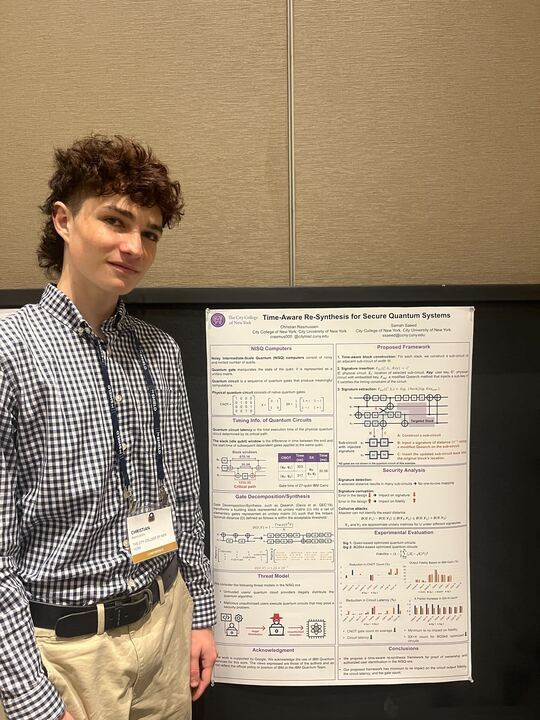

The director of the SERS Lab is Prof. Samah Mohamed Ahmed Saeed, who is an assistant professor in the electrical engineering department at Grove School of Engineering at CCNY, City University of New York. Prof. Saeed received her Ph.D. in the Computer Science and Engineering Department, New York University Tandon School of Engineering. Her research interests include the security and the reliability of quantum systems, hardware security, and testing VLSI circuits. Her research has been recognized through several awards including the best paper award at IEEE VLSI Test Symposium, the Pearl Brownstein Doctoral Research Award by NYU Polytechnic School of Engineering, and […]

Mission of the SERS Lab

We are a research team in CCNY, whose main focus is the system reliability and security. Our research spans from classical to quantum computing systems. Our mission is to enable reliable and secure breakthrough applications for quantum and classical systems by making them more resilient to errors during mission mode and expose any malicious activities that leak sensitive information or change the functionality.